传统式、背照式、堆栈式CMOS传感器的区别

前照式CMOS

传统的CMOS真正名称为前照式CMOS(FrontSide lllumination,缩写为FSI)。

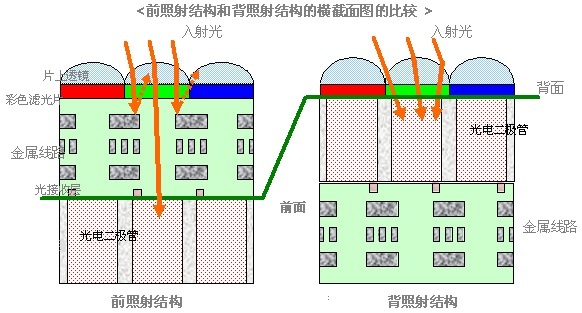

一般的CMOS像素由一下几部分构成:片上透镜、彩色滤光片、金属排线、光电二极管以及基板。传统的CMOS是左图中的前照式结构,当光线射入像素,经过了片上透镜和彩色滤光片后,先通过金属排线层,最后光线才被光电二极管接收。

在金属排线这层光线会被部分阻挡和反射,光电二极管吸收的光线就会减少,而且反射还有可能串扰旁边的像素,导致颜色失真。(目前中低档的CMOS排线层用的是比较廉价的铝,铝对整个可见光波段(380~780nm)基本保持在90%左右的反射率)

背照式CMOS

背照式CMOS(Back-Illuminated CMOS)的金属排线和光电二极管的位置和前照式正好相反,光线几乎没有被阻挡和干扰下到光电二极管,

自上至下依次为微透镜(Micro-lens)、彩色滤光镜(Color Filter)、光电二极管(Photodiodes)和电路层(Wiring Layers)。

光线利用率极高,所以背照式CMOS传感器能更好的利用照射入的光线,在低照度环境下成像质量更好。

由于电路层变得密度更高,电路和电路之间不可避免地会产生干扰。其结果就是低感光度下的信噪比可能会有所下降。

相比起普通的传感器,搭载背照式传感器的摄像头能够在弱光环境下,提高约30%—50%的感光能力,能够在弱光下拍摄更高的质量的照片。

堆栈式CMOS

堆栈式CMOS最先出现在索尼退出的移动终端用CMOS上,堆栈式出现的初衷其实不是为了减少整个镜头模组的体积,这个只是其附带好处。

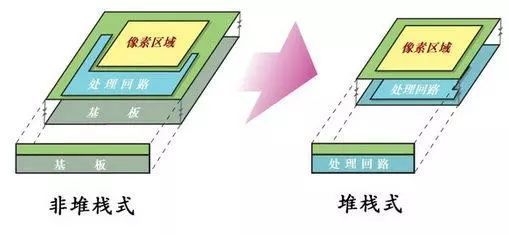

CMOS的制作和CPU的制作类似,需要特殊的光刻机对硅晶圆进行蚀刻,形成像素区域(Pixel Section)和处理回路区域(Circuit Section)。像素区域就是种植像素的地方,而处理回路就是管理这群像素的电路。

为了提高像素集合光的效率,需要引入光波导管。光波导管在干刻过程中,硅晶圆和像素区域会有损伤,此时要进行一个”退火”的热处理步骤,让硅晶圆和像素区域从损伤中恢复出来,这时候需要将整块CMOS加热。那么这么一加热,同一块晶圆上的处理回路肯定有一定的损伤,原先已经“打造”好的电容电阻值,经过退火后肯定改变了,这种损伤必定会对电信号读出有一定影响。

还有一个问题,索尼目前建有的移动终端用CMOS的制程是65nm干刻,65nm的工艺对于CMOS的像素区域“种植”是完全足够的。但是主力回路区域的“打造”,65nm是不够的,如果能有30nm(实际提升至45nm制程)的工艺去打造电路,那么处理回路上的晶体管数量几乎翻倍,其对像素区域的”调教”也会有质的飞越,画质肯定会相应变好。但因为是在同一块晶圆上制作,像素和回路区域需要在同一制程下制作。

原来处理回路和像素区域在同一块晶圆上打造的。那么不妨把处理回路放到其他地方去。

首先利用SOI和基板的热传导系数差异,通过加热将两者分开。像素区域放到65nm制程的机器上做,处理回路则放到制程更高(45nm)的机器上做。然后拼在一起,堆栈式CMOS就此诞生。

前面提到的两个问题也就迎刃而解:

- 像素“退火”时回路区域受影响

- 在同一块晶圆上制作时的制程限制

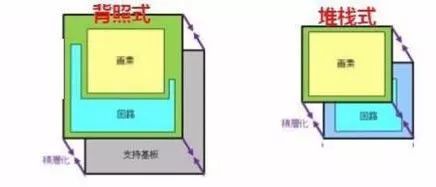

堆栈式不仅继承了背照式的优点(像素区域依然是背照式),还克服了其在制作上的限制和缺陷。由于处理回路的改善和进步,摄像头也将提供更多的功能,比如硬件HDR,慢动作拍摄等。

像素和处理回路分家的同时,摄像头体积也会变得更小,但功能和性能却不减,反而更佳。像素区域(CMOS尺寸)可以相应地增大,用来种植更多或更大的像素。处理回路也会得到相应的优化。

堆栈式CMOS使用有信号处理电路的芯片代替感光组件的电路部分及支持基板,使得设备有极大的空间,在此形成更多的像素部分,同时采用堆栈的方式使像素部分和电路芯片重叠,堆栈的两层相互依赖,像素层与模拟逻辑芯片无需再互抢所占空间,两者相互独立,可单独提高像素质量及电路性能。

堆栈式CMOS优点:

堆栈式由背照式发展而来,背照式传感器是将感光层的光电二极管的位置互换一下,而堆栈式传感器则是把信号回路位置互换。而且堆栈式传感器比背照式的体积更小,画质方面也是作了更好的优化。

此外堆栈式相比背照式还有两项技术来提升画质:

第一个是堆栈式传感器加入了RGBW的编码技术,由原来的R、G、B三原色像素点再加入W(白)像素点来提升画质,提高传感器的感光能力,使摄像头在暗光环境下也能拍质量更高的照片。

第二就是堆栈式传感器更加支持硬件HDR(In-camera HDR)功能,原理是能够精确地单独控制每一行像素的曝光时间,从而在传感器层面上就实现原生的高动态范围渲染,有别于之前的软件HDR技术一样需要软件,照相机综合算法来合成,所以照片生成速度更快,而且可以实现HDR录像。